Языки описания аппаратных средств – это универсальные алгоритмические языки; это языки, способные описывать параллельно протекающие во времени процессы; это языки, способные поддерживать множество стилей описания аппаратуры и инженерных приложений. Применяемые к проектированию электронных устройств, они позволяют ускорить процесс создания последних, а так же, значительно снизить их себестоимость.

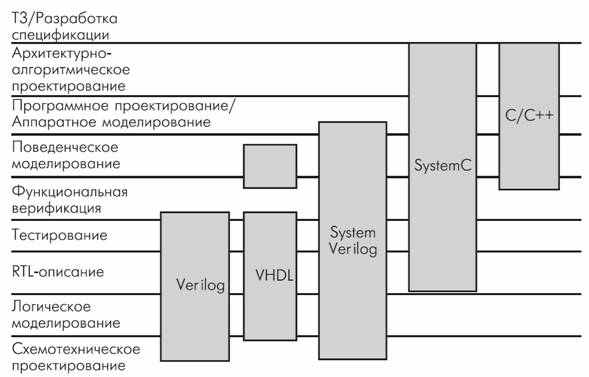

Интенсивный прогресс в области микроэлектроники привел в последние годы к появлению нового класса СБИС – «Систем на кристалле» (СнК), которые содержат программируемые процессорные ядра, специализированные логические блоки, модули памяти, интерфейсные и периферийные устройства, аналоговые и аналого-цифровые схемы [7]. Степень интеграции современных СнК достигает нескольких десятков миллионов вентилей на кристалле, и для их разработки и моделирования необходимы новые подходы, методы и системы проектирования. Для реализации полного цикла проектирования СнК используется определенный набор программных продуктов и языков программирования. На «рисунке 1.1» приведены основные этапы проектирования СнК и различные языки и средства разработки, используемые для выполнения этих этапов.

Рисунок 1.1 – Основные этапы проектирования «Систем на кристалле» и области применения современных средств и языков программирования

Язык высокого уровня C++ используется в качестве основного средства разработки программного обеспечения и создания моделей высокого уровня абстракции (поведенческие модели «Систем на кристалле»). Основные достоинства C++ - это низкая стоимость средств программирования, простота в освоении и использовании. Главный недостаток связан с отсутствием специализированных библиотек системного уровня, поэтому поведенческую модель разработчику приходится создавать практически «с нуля».

Существует огромное количество языков описания аппаратных средств. Но в настоящее время наиболее распространенными и часто используемыми являются VHDL, Verilog, System Verilog и SystemC.

Языки описания аппаратуры (HDL-языки) имеют две основные разновидности – языки низкого уровня (аналоги языков программирования типа ассемблера) и высокого уровня [4]. Языки низкого уровня ближе к аппаратным средствам, вследствие чего представляют для компиляторов потенциальные возможности создания проектов с более выигрышными параметрами. Платой за это является обычно жесткая ориентация на определенную аппаратуру и призводящую ее фирму. Примерами таких языков могут служить языки PLDASM (фирма Intel), AHDL (Фирма Altera) и ABEL (Фирма Zilinx). Языки высокого уровня менее связаны с аппаратными платформами и поэтому более универсальны. Среди них наиболее распространены языки VHDL и Verilog. Эти языки, как и другие алгоритмические языки высокого уровня, в принципе позволяют описать любой алгоритм в последовательной форме, т.е. через последовательность операторов присвоения и принятия решений. Основное их отличие в способности отражать также и параллельно исполняемые в аппаратуре действия, представляемые отдельными параллельно выполняемыми процессами с общим инициализирующим воздействием. Совсем недавно был создан язык HDL-уровня - System Verilog. Это новый язык описания аппаратуры, созданный на базе Verilog и C++. Он призван расширять возможности классического языка описания Verilog и дает возможность проводить моделирование как на функциональном, так и на системном уровне. SystemC, как и System Verilog, разрабатывался как единый язык проектирования, способный обеспечить выполнение архитектурного моделирования и возможность синтеза разработанной системы.

1.1. Язык VHDL

Язык VHDL появился в начале 80-х годов по заказу организации Министерства обороны США [4]. Первая его версия, предназначенная в основном для унификации описаний проектов в различных ведомствах, была принята в 1985 году. В 1987 году язык VHDL был принят Международным институтом IEEE как стандарт VHDL-87. Он использовался, главным образом, для описания (спецификации) уже спроектированных систем. Использование для задач синтеза устройств (работа с компиляторами) началось с 1991 года. В 1993 году IEEE принял новый расширенный стандарт VHDL-93.

Язык может быть использован для проектирования ЦА разных иерархических уровней – от вентильного до системы в целом. В 1999 году был утвержден стандарт языка IEEE Std 1076.1-1999, известного под названием VHDL-AMS. Это расширение языка VHDL ориентировано на описание аналоговых и смешанных (аналого-йифровых) устройств. В настоящее время язык VHDL является самым популярным среди проектировщиков цифровой аппаратуры.

Язык VHDL является проблемно-ориентированным, его основные прикладные аспекты связаны с использованием в качестве рабочего инструмента для задач описания структуры и (или) поведения широкого класса цифровых устройств. Описания могут использоваться для синтеза и (или) моделирования таких схем. В соответствии с назначением, язык приспособлен для описания систем как с точки зрения их структурной организации (из модулей с известным поведением), так с точки зрения поведения либо системы в целом, либо всех его составных частей.

Синтаксические конструкции языка содержат две составляющие – общеалгоритмическую и проблемно-ориентированную.

Общеалгоритмическая состовляющая языка достаточно традиционна и содержит как традиционные операторы действия (присваивание :=), условия (IF), выбора (CASE), цикла (LOOP), вызова процедуры), так и традиционные типы данных: числовые, логические, символьные, перечислительные и агрегатированные (массивы, записи, файлы).

VHDL поддерживает три различных стиля для описания аппаратных архитектур. Первый из них — структурное описание (structural description), в котором архитектура представляется в виде иерархии связанных компонентов. Второй — потоковое описание (data-flow description), в котором архитектура представляется в виде множества параллельных регистровых операций, каждая из которых управляется вентильными сигналами. Потоковое описание соответствует стилю описания, используемому в языках регистровых передач. И, наконец, поведенческое описание (behavioral description), в котором преобразование описывается последовательными программными предложениями, которые похожи на имеющиеся в любом современном языке программирования высокого уровня. Все три стиля могут совместно использоваться в одной архитектуре.

Каждый объект проекта состоит, как минимум, из двух различных типов описаний: описания интерфейса и одного или более архитектурных тел. Интерфейс описывается в объявлении объекта (entity declaration) и определяет только входы и выходы объекта.

Для описания поведения объекта или его структуры служит архитектурное тело (architecture body). Чтобы задать, какие объекты использованы для создания полного проекта, используется объявление конфигурации (configuration declaration).

В языке VHDL предусмотрен механизм пакетов для часто используемых описаний, констант, типов, сигналов. Эти описания помещаются в объявление пакетов (package declaration). Если пользователь использует нестандартные операции или функции, их интерфейсы описываются в объявлении пакета, а тела содержатся в теле пакета (package body).

Язык VHDL является очень распространенным языком описания аппаратуры. Существует множество литературы, в том числе и на русском языке, посвященной этому высококлассному средству разработки аппаратуры, что делает его очень доступным для обучения.

1.2. Язык Verilog

Язык Verilog был разработан фирмой Gateway Design Automaton как внутренний язык симуляции [8]. Cadence приобрела Gateway в 1989 г. и открыла Verilog для общественного использования. В 1995 г. был определен стандарт языка — Verilog LRM (Language Reference Manual), IEEE1364-1995. Таким образом, датой появления языка Verilog следует считать 1995 г. К этому времени уже успел получить широкое распространение другой язык высокого уровня для описания принципиальных схем — VHDL, появившийся еще в 1987 г. Несмотря на похожие названия, Verilog HDL и VHDL — различные языки. Verilog — достаточно простой язык, сходный с языком программирования С как по синтаксису, так и по «идеологии». Малое количество служебных слов и простота основных конструкций упрощают изучение и позволяют использовать Verilog в целях обучения. Но в то же время это эффективный и специализированный язык. VHDL обладает большей универсальностью и может быть использован не только для описания моделей цифровых электронных схем, но и для других моделей (например, модели экосистемы). Однако из-за своих расширенных возможностей VHDL проигрывает в эффективности и простоте, то есть на описание одной и той же конструкции в Verilog потребуется в 3–4 раза меньше символов (ASCII), чем в VHDL.

В Verilog существуют специфические объекты (UDP, Specify-блоки), не имеющие аналогов в VHDL. Также следует упомянуть стандарт PLI (Program Language Interface), который позволяет включать функции, написанные пользователем (например, на С), в код симулятора.

Основной структурной единицей Verilog описания является module. Модуль соответствует entity в VHDL. Модуль описывается ключевыми словами module — endmodule. В файле может быть описано несколько модулей. Другие модули могут подключаться к цепям модуля, образуя иерархическую структуру. При запуске Verilog симулятор строит иерархическое дерево из всех модулей, которые обнаружены в файлах, поданных на вход симулятора, и находит модуль верхнего уровня. Если таких модулей несколько, то происходит ошибка. Как правило, модуль содержит список портов — интерфейсных сигналов, которые служат для подключения его в других модулях. Порты бывают трех типов input — входы, output — выходы, inout — двунаправленные. Входы и двунаправленные порты должны иметь тип wire, а выходы могут быть как wire, так и reg. Построение иерархии (подключение модулей) возможно двумя способами: по имени (указываются имена портов, использованные при описании модуля) или по расположению (порядок сигналов такой же, как в описании модуля).

В настоящее время фактором, препятствующим быстрому изучению языка Verilog, является то, что этому языку посвящено не так много литературы, особенно на русском языке.

1.3. Язык SystemC

Необходимость создания нового языка описания аппаратуры возникает в том случае, если существующие языки не способны решать возникающие задачи. С одной из трудноразрешимых задач столкнулись самые популярные и распространенные языки VHDL и Verilog – это постоянно растущая сложность разрабатываемых проектов и необходимость в универсальном способе описания, пригодного для всех уровней проектирования и независимого от формы реализации проектов [4]. Попыткой решить возникшие трудности стало использование языка SystemC.

В 1999 году вышла в свет первая версия библиотеки SystemC 0.9. С этого времени можно считать появление языка SystemC. В настоящее время последняя версия данного продукта 2.2. Ассоциацией Стандартов IEEE одобрен стандарт библиотеки SystemC std. IEEE 1666 ™-2005 [1].

SystemC представляет собой надстройку стандартного языка программирования С++, реализованную в виде отдельных библиотек специальных классов. Данные библиотеки содержат в себе конструкции, позволяющие создавать эффективные и точные модели программных алгоритмов, аппаратных архитектур, интерфейсов и схем на системном уровне, т.е. практически всех компонентов встроенных систем [6]. Такой подход имеет значительный потенциал, так как основан на однородном описании С++ и легко позволяет моделировать, тестировать системы, рассматривать альтернативные архитектуры. Кроме того, команде проектировщиков может быть предложено развёрнутое описание процесса работы всей системы. Это описание представляет собой программу С++, которая при исполнении ведёт себя так же, как и система.

Основная цель в использовании данного языка – добиться сокращения времени разработки СнК [7]. Это достигается за счет исключения из процесса проектирования этапа перехода с одного языка описания на другой, который не требуется при использовании традиционной методики разработки сложнофункциональных СБИС для перехода от поведенческой модели на языке C++ к синтезируемой RTL-модели на HDL-языке.

|

![]()

![]()