4.1. Разработка модели мультиплексора на 4 входа

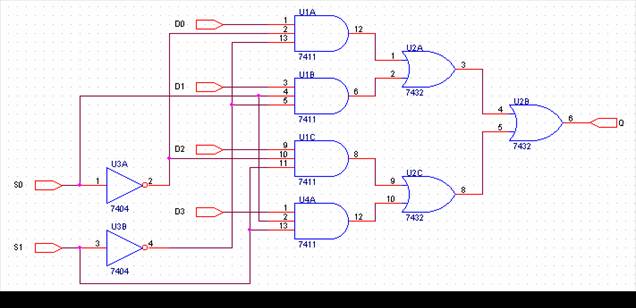

С помощью Active-HDL 7.1 начнем создание структурной модели мультиплексора на 4 входа, структурная схема которого представлена на «рисунке 4.1».

Рисунок 4.1 – Структурная схема мультиплексора на 4 входа

4.1.1. Разработка моделей логических элементов

Для реализации структурной модели нам потребуются логические элементы: НЕ 7404, 2ИЛИ 7432, и 3И 7411. С помощью “New Source File Wizzard” создадим модель каждого из перечисленных элементов:

- Инвертор 7404. Файл inv.h:

#ifndef __inv_h__

#define __inv_h__

#include <systemc.h>

SC_MODULE( inv )

{

sc_in< bool > A;

sc_out< bool > F;

sc_event delay;

SC_CTOR( inv ):

A("A"),

F("F")

{

SC_METHOD(do_delay);

sensitive << A;

SC_METHOD(do_inv);

sensitive << delay;

}

void do_delay(){delay.notify(22, SC_NS);}

void do_inv(){F.write( !A.read() );}

};

SC_MODULE_EXPORT( inv )

#endif

#ifndef __or2_h__

#define __or2_h__

#include <systemc.h>

SC_MODULE( or2 )

{

sc_in< bool > A, B;

sc_out< bool > F;

sc_event delay;

SC_CTOR( or2 ):

A("A"),

B("B"),

F("F")

{

SC_METHOD(do_delay);

sensitive << A << B;

SC_METHOD(do_or2);

sensitive << delay;

}

void do_delay(){delay.notify(22, SC_NS);}

void do_or2(){F.write( A.read() || B.read() );}

};

SC_MODULE_EXPORT( or2 )

#endif

#ifndef __and3_h__

#define __and3_h__

#include <systemc.h>

SC_MODULE( and3 )

{

sc_in< bool > A, B, C;

sc_out< bool > F;

sc_event delay;

SC_CTOR( and3 ):

A("A"),

B("B"),

C("C"),

F("F")

{

SC_METHOD(do_delay);

sensitive << A << B << C;

SC_METHOD(do_and3);

sensitive << delay;

}

void do_delay(){delay.notify(27, SC_NS);}

void do_and3(){F.write( A.read() && B.read() && C.read() );}

};

SC_MODULE_EXPORT( and3 )

#endif

4.1.2. Разработка иерархического блока mux4

Создадим иерархический блок mux4, который будет включать в себя вышеперечисленные элементы, и приведем подробное описание кода заголовочного файла (mux4.h):

#ifndef __mux4_h__

#define __mux4_h__

#include <systemc.h>

// Подключение заголовочных файлов с описанием элементов НЕ, 2ИЛИ, 3И.

#include "inv.h"

#include "or2.h"

#include "and3.h"

SC_MODULE( mux4 )

{

sc_in< bool > D0, D1, D2, D3, S0, S1; // Входные порты

sc_out< bool > F; // Выходной порт

sc_signal <bool> NS0, NS1, A1, A2, A3, A4, O1, O2; // Внутренние сигналы модуля

// Объявление объектов

inv n1, n2;

or2 o1, o2, o3;

and3 a1, a2, a3, a4;

// Конструктор. Задание имен объектам модуля. Cигналам и портам не обязательно.

SC_CTOR( mux4 ):

D0("D0"), D1("D1"), D2("D2"), D3("D3"),

S0("S0"), S1("S1"),

F("F"),

n1("not1"), n2("not2"),

a1("and1"), a2("and2"), a3("and3"), a4("and4"),

o1("or1"), o2("or2"), o3("or3")

{

// Структурное описание работы мультиплексора. Запись n1 << S0 << NS0

// означает, что на вход A инвертора подается сигнал S0, а сигналу

// NS0 присваивается результат работы инвертора.

n1 << S0 << NS0;

n2 << S1 << NS1;

a1 << D0 << NS0 << NS1 << A1;

a2 << D1 << S0 << NS1 << A2;

a3 << D2 << NS0 << S1 << A3;

a4 << D3 << S0 << S1 << A4;

o1 << A1 << A2 << O1;

o2 << A3 << A4 << O2;

o3 << O1 << O2 << F;

}

};

SC_MODULE_EXPORT( mux4 )

#endif

Также необходимо создать файл mux4.cpp и поместить в него строку: #include “mux4.h”.

4.1.3. Тестирование проекта

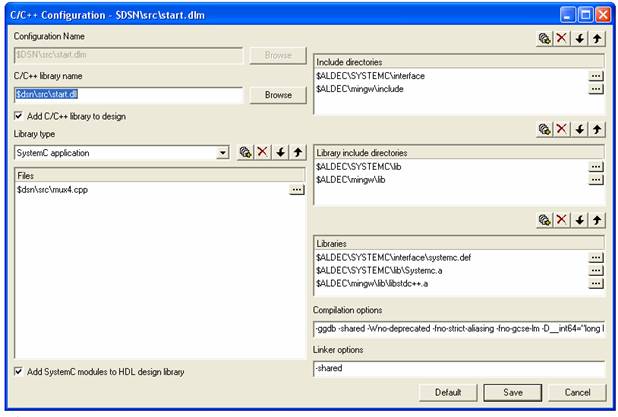

Чтобы откомпилировать проект, необходимо создать файл конфигурации С/С++ через “File -> New -> C/C++ Configuration”. Назовем его “start.dlm”. Диалоговое окно с необходимыми настройками для конфигурационного файла изображено на «рисунке 4.2».

Рисунок 4.2 – Настройки для конфигурационного файла “start.dlm”

Далее можно приступать к компиляции проекта, для этого необходимо нажать правой кнопкой по конфигурационному файлу “start.dlm” и выбрать “Build”. Если компиляция прошла без ошибок, то можно переходить к этапу верификации проекта.

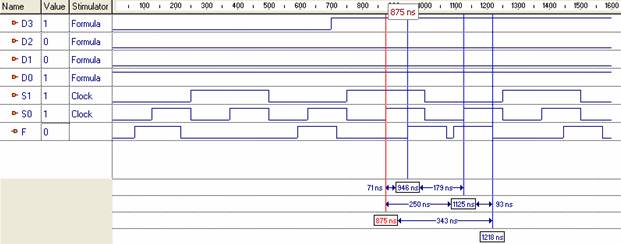

Выберем созданную модель мультиплексора mux4 в окне структуры проекта (Design Browser – Structure). Создадим временную диаграмму, нажав на кнопку “New Waveform” и добавим сигналы D0, D1, D2, D3, S0, S1, F. Зададим входные сигналы для D0, D1, D2, D3, S0 и S1 следующим образом:

- D0 (Formula): 0 0 ns, 1 700 ns;

- D1 (Formula): 0 0 ns;

- D2 (Formula): 0 0 ns;

- D3 (Formula): 1 0 ns;

- S0 (Clock): 2MHz;

- S1 (Clock): 4MHz.

Запустим моделирование на промежутке времени 1,6 us и получим временную диаграмму работы мультиплексора, изображенную на «рисунке 4.3».

Рисунок 4.3 – Результат моделирования проекта mux4

Полное описание проекта мультиплексора на 4 входа, разработанного в среде MS Visual Studio 2005, находится в «приложении 1».

4.2. Разработка модели цифрового автомата

С помощью Active-HDL 7.1 начнем создание модели цифрового автомата, имеющего два режима работы. Конкретный режим задается значением сигнала на входе M (от слова Mode - режим):

- При M = 0 цифровой автомат выполняет функцию счетчика Джонсона;

- При M = 1 цифровой автомат выполняет функцию счетчика с произвольным порядком счета 0_2_4_6_8_3_1_0;

- Число разрядов n = 4;

- Тип триггеров - JK;

- Сброс R = 1 (высоким уровнем);

- Счет по срезу сигнала С.

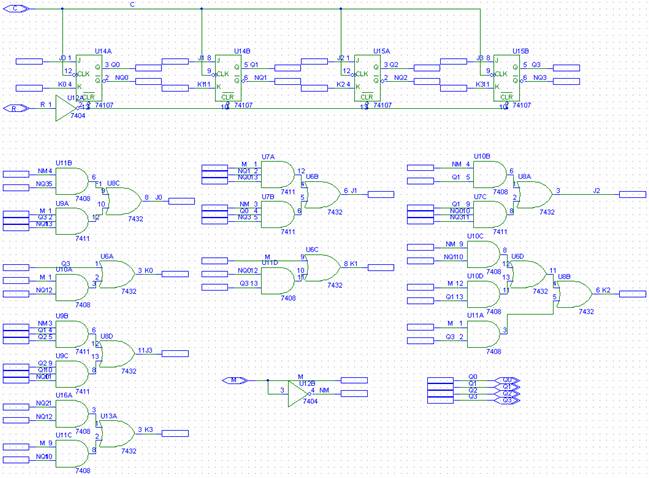

Структурная схема цифрового автомата “Jonson_02468310” представлена на «рисунке 4.4».

Рисунок 4.4 – Структурная схема цифрового автомата “Jonson_02468310”

4.2.1. Разработка моделей составных элементов ЦА

Модели логических элементов НЕ 7404, 2ИЛИ 7432, 3И 7411 были разработаны в предыдущем примере, опустим также описание модели элемента 2И 7408. Приведем описание модели JK-триггера 74017 (файл jk_trigger.h):

#ifndef __jk_trigger_h__

#define __jk_trigger_h__

#include <systemc.h>

SC_MODULE(jk_trigger)

{

sc_in <bool> J, K, Clock, Reset;

sc_out <bool> F, NF;

bool fall;

int count;

sc_event trigger_switch;

SC_CTOR(jk_trigger):

J("J"),

K("K"),

Clock("Clock"),

Reset("Reset"),

F("F"),

NF("NF")

{

count = 0;

SC_METHOD(do_reset);

sensitive << Reset.neg();

SC_METHOD(do_jk);

sensitive << Clock.neg();

SC_METHOD(do_switch);

sensitive << trigger_switch;

}

void do_switch()

{

if(count < 2)return;

if(fall){F.write(true); NF.write(false);}

else {F.write(false); NF.write(true);}

}

void do_jk()

{

if(F.read() != NF.read())

{

if(J.read() == true && K.read() == true)

{

if(F.read() == true)

{

fall = false;

trigger_switch.notify(25, SC_NS);

}

else

{

fall = true;

trigger_switch.notify(40, SC_NS);

}

}

}

if(J.read() == true && K.read() == false)

{

if(F.read() == false)fall = true;

trigger_switch.notify(40, SC_NS);

}

if(J.read() == false && K.read() == true)

{

if(F.read() == true)fall = false;

trigger_switch.notify(25, SC_NS);

}

}

void do_reset()

{

count++;

fall = false;

trigger_switch.notify(25, SC_NS);

}

};

SC_MODULE_EXPORT( jk_trigger )

#endif //__jk_trigger_h__

4.2.2. Разработка иерархического блока цифрового автомата

Приведем описание иерархического блока Jonson_02468310 (файл Jonson_02468310.h), который будет включать в себя все модели элементов, описанных в предыдущих пунктах работы:

#ifndef __Jonson_02468310_h__

#define __Jonson_02468310_h__

#include <systemc.h>

#include "inv.h"

#include "or2.h"

#include "and2.h"

#include "and3.h"

#include "jk_trigger.h"

SC_MODULE( Jonson_02468310 )

{

sc_in <bool> M, R, C;

sc_out <bool> Q0, Q1, Q2, Q3, NQ0, NQ1, NQ2, NQ3;

sc_signal <bool> J[4], K[4], NR, NM;

sc_signal <bool> I[16];

and2 A2_0, A2_1, A2_2, A2_3, A2_4, A2_5, A2_6, A2_7, A2_8;

and3 A3_0, A3_1, A3_2, A3_3, A3_4, A3_5;

or2 O2_0, O2_1, O2_2, O2_3, O2_4, O2_5, O2_6, O2_7, O2_8;

inv N_0, N_1;

jk_trigger JK_0, JK_1, JK_2, JK_3;

SC_CTOR( Jonson_02468310 ):

M("M"), R("R"), C("C"), Q0("Q0"), Q1("Q1"), Q2("Q2"), Q3("Q3"),

NQ0("NQ0"), NQ1("NQ1"), NQ2("NQ2"), NQ3("NQ3"),

A2_0("AND2_0"), A2_1("AND2_1"), A2_2("AND2_2"),

A2_3("AND2_3"), A2_4("AND2_4"), A2_5("AND2_5"),

A2_6("AND2_6"), A2_7("AND2_7"), A2_8("AND2_8"),

O2_0("OR2_0"), O2_1("OR2_1"), O2_2("OR2_2"),

O2_3("OR2_3"), O2_4("OR2_4"), O2_5("OR2_5"),

O2_6("OR2_6"), O2_7("OR2_7"), O2_8("OR2_8"),

A3_0("AND3_0"), A3_1("AND3_1"), A3_2("AND3_2"),

A3_3("AND3_3"), A3_4("AND3_4"), A3_5("AND3_5"),

N_0("N_0"), N_1("N_1"), JK_0("JK_0"),

JK_1("JK_1"), JK_2("JK_2"), JK_3("JK_3")

{

N_0 << R << NR; N_1 << M << NM;

A2_0 << NM << NQ3 << I[0]; A3_0 << M << Q3 << NQ1 << I[1];

O2_0 << I[0] << I[1] << J[0]; A2_1 << M << NQ1 << I[2];

O2_1 << Q3 << I[2] << K[0]; A3_1 << NM << Q1 << Q2 << I[3];

A3_2 << Q2 << Q1 << NQ0 << I[4]; O2_2 << I[3] << I[4] << J[3];

A2_2 << NQ2 << NQ1 << I[5]; A2_3 << M << NQ1 << I[6];

O2_3 << I[5] << I[6] << K[3]; A3_3 << M << NQ1 << NQ0 << I[7];

A3_4 << NM << Q0 << NQ3 << I[8]; O2_4 << I[7] << I[8] << J[1];

A2_4 << NQ0 << Q3 << I[9]; O2_5 << M << I[9] << K[1];

A2_5 << NM << Q1 << I[10];

A3_5 << Q1 << NQ0 << NQ3 << I[11];

O2_6 << I[10] << I[11] << J[2]; A2_6 << NM << NQ1 << I[12];

A2_7 << M << Q1 << I[13]; O2_7 << I[12] << I[13] << I[14];

A2_8 << M << Q3 << I[15]; O2_8 << I[14] << I[15] << K[2];

JK_0 << J[0] << K[0] << C << NR << Q0 << NQ0;

JK_1 << J[1] << K[1] << C << NR << Q1 << NQ1;

JK_2 << J[2] << K[2] << C << NR << Q2 << NQ2;

JK_3 << J[3] << K[3] << C << NR << Q3 << NQ3;

}

};

SC_MODULE_EXPORT( Jonson_02468310 )

#endif

4.2.3. Тестирование проекта

Чтобы откомпилировать проект, необходимо создать файл конфигурации С/С++ через “File -> New -> C/C++ Configuration”. Назовем его “start.dlm”. В «пункте 4. 1. 3» данной работы приведены настройки, которые необходимы для правильной работы.

Далее можно приступать к компиляции проекта, для этого необходимо нажать правой кнопкой по конфигурационному файлу “start.dlm” и выбрать “Build”. Если компиляция прошла без ошибок, то можно переходить к этапу верификации проекта.

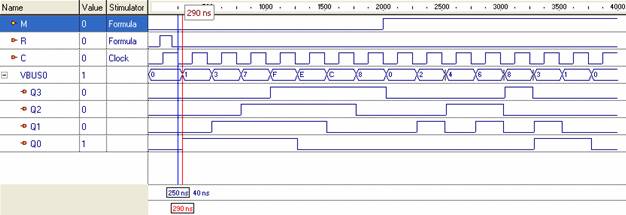

Выберем созданную модель мультиплексора Jonson_02468310 в окне структуры проекта (Design Browser – Structure). Создадим временную диаграмму, нажав на кнопку “New Waveform” и добавим сигналы M, R, C, Q3, Q2, Q1, Q0. Для удобства объединим сигналы Q3, Q2, Q1, Q0 в шину. Зададим входные сигналы для M, R и C следующим образом:

- M (Formula): 0 0 ns, 1 2000 ns;

- R (Formula): 0 0 ns, 1 100 ns, 0 200 ns;

- C (Clock): 4MHz.

Запустим моделирование на промежутке времени 4 us и получим временную диаграмму работы цифрового автомата Jonson_02468310, изображенную на «рисунке 4.5».

Рисунок 4.5 – Результат моделирования проекта Jonson_02468310

Полное описание проекта цифрового автомата Jonson_02468310, разработанного в среде MS Visual Studio 2005, находится в «приложении 2».

|

![]()

![]()